課題:IRドロップ検証・電源インピーダンス検証

基板の抵抗成分で発生するIRドロップ(電圧降下)や電源インピーダンス特性、同時スイッチングノイズの影響などを設計段階で把握・対策できるため、信頼性の高い製品開発につながります。システムの電気特性を改善にするには電源ノイズを低減することが有効であり、幅広い分野の基板設計を手掛けてきた当社が、確かな製品設計を支えます。

主な対応可能項目

-

DC解析

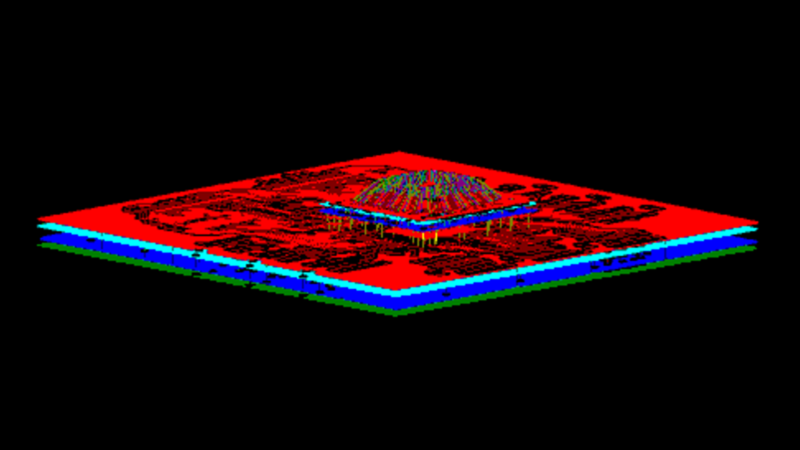

・多ピンBGAのVIA周囲で発生する電圧降下の事前検証と最適化

・回路の多電源化に伴う電源層の検証と最適化

・電源供給元からICの電源元までの経路におけるDC抵抗を算出し、規定の電圧変動以内とするための最適化

・ボード、パッケージ、チップの接続端子数の最適化 -

AC解析

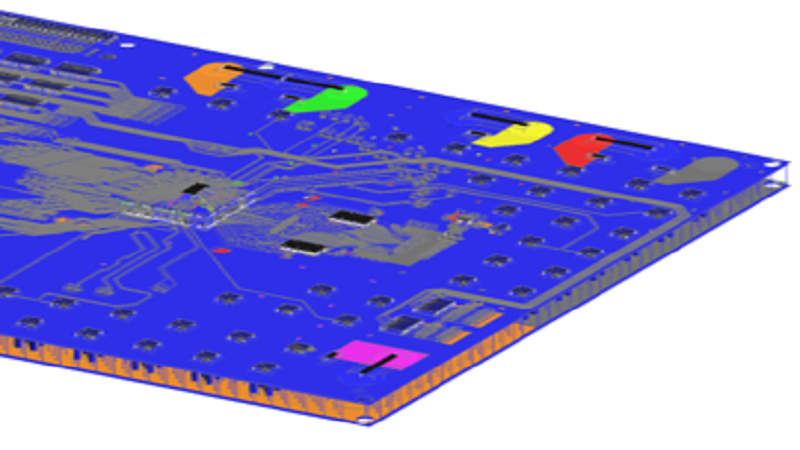

・電源インピーダンス/ループインダクタンスの周波数特性解析

・バイパスコンデンサの配置と容量の最適化

・信号配線と電源配線の結合を考慮したスイッチングノイズ解析と最適化

・モーター制御等の低周波領域における大電流回路の電源インピーダンスおよびノイズ解析

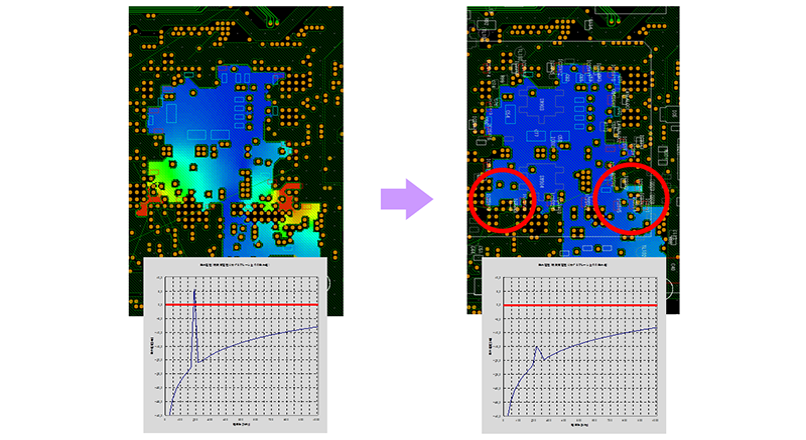

【シミュレーション事例】電源プレーンの共振解析とプレーンの形状を最適化を行い電源ノイズを低減

関連事例

PI(Power Integrity)シミュレーションの導入事例をご紹介します。