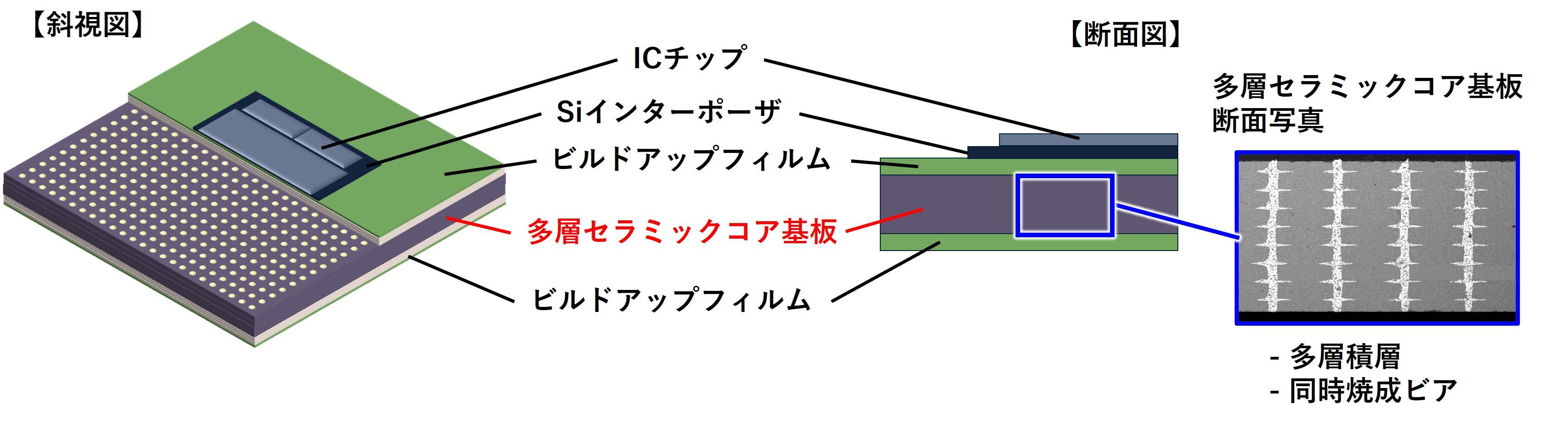

先端半導体の高性能化に伴い、シリコン等のインターポーザ上に複数のICチップを実装する技術(チップレット)が普及しています。

この高性能化のため、チップレット実装に用いるインターポーザが大型化、それに伴い、インターポーザを実装するパッケージ基板も大型化が進んでいます。

京セラは、そのパッケージ基板として適した高剛性/高強度の多層セラミックコア基板を開発しています。

概要

多層セラミックコア基板使用イメージ

京セラは多層セラミックコア基板のみの供給になります。

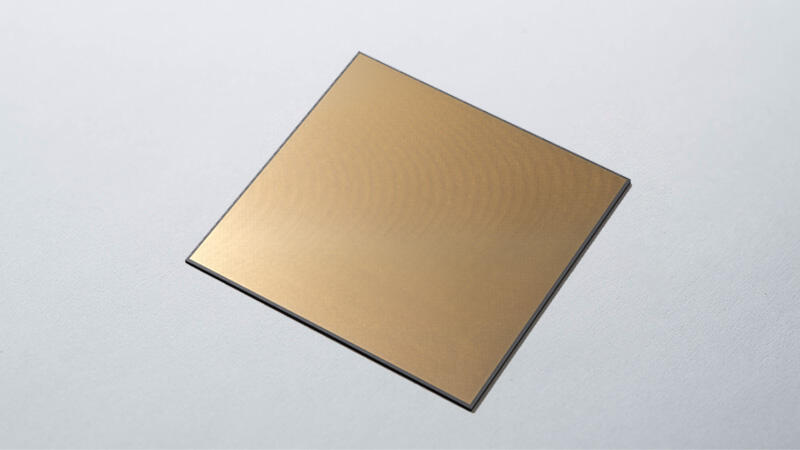

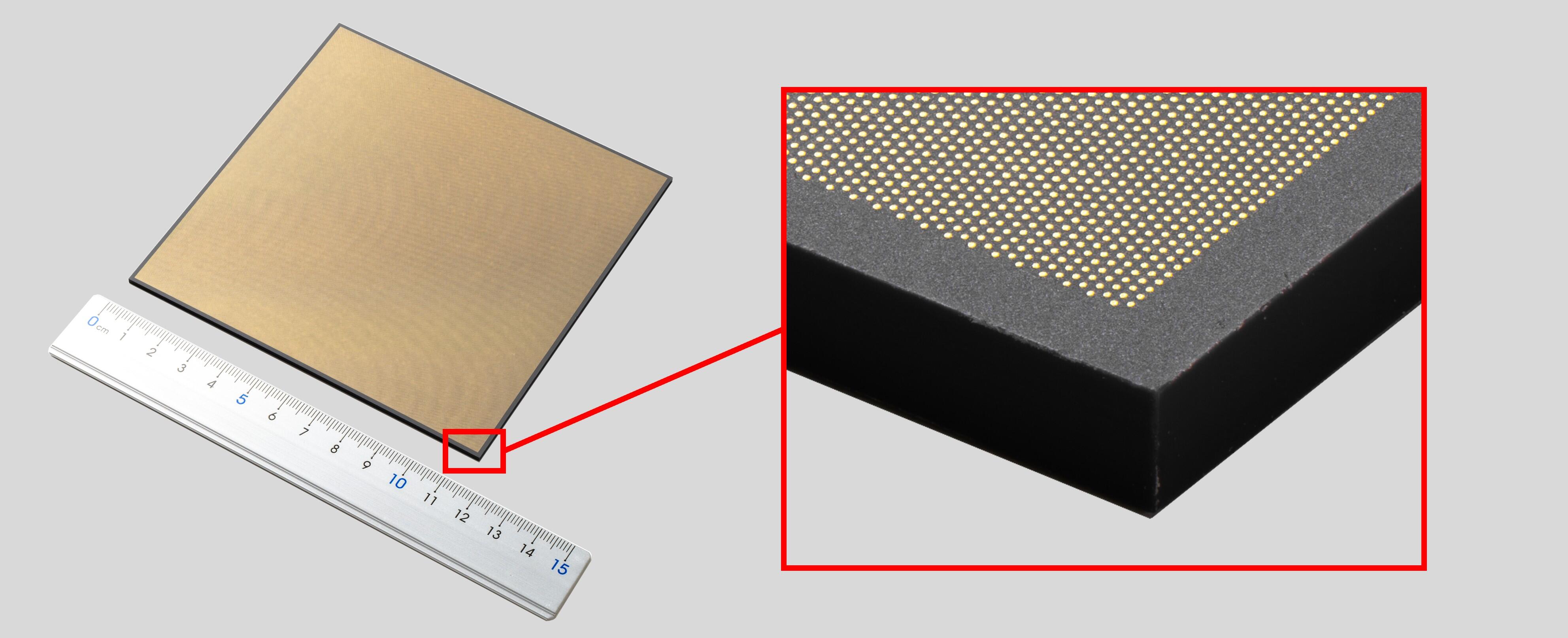

多層セラミックコア基板サンプル写真

ビア径75µm、ビアピッチ200µm

特長

高剛性

熱による変形が少ない

薄型化

熱膨張係数のマッチング

基板反りを抑制できる高剛性(高ヤング率)、熱応力に耐えられる高強度

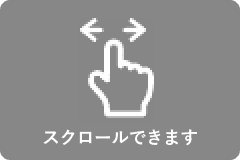

先端半導体向けの大型パッケージ基板はコア基板にビルドアップフィルムを積層して製造しますが、ビルドアップフィルム積層時の応力、チップレット実装時の応力で反りやすくなるため、コア材は高ヤング率の材料を使い、反りを低減する必要があります。また、実装時の熱応力によってコア基板が割れないように高強度である必要があります。

一般的な大型パッケージ基板の機材として主流の有機コア材では剛性不足で生じるチップレット実装後の「反り」低減が、代替として検討されているガラスコア材では「セワレ(※)」の防止が課題となっています。京セラは、これらを解決する高剛性/高強度の多層セラミックコア基板を開発しています。

(※)セワレ:ビルドアップフィルム積層時やICチップ実装時の応力に対し、コア基板の強度不足で生じるコア材破壊

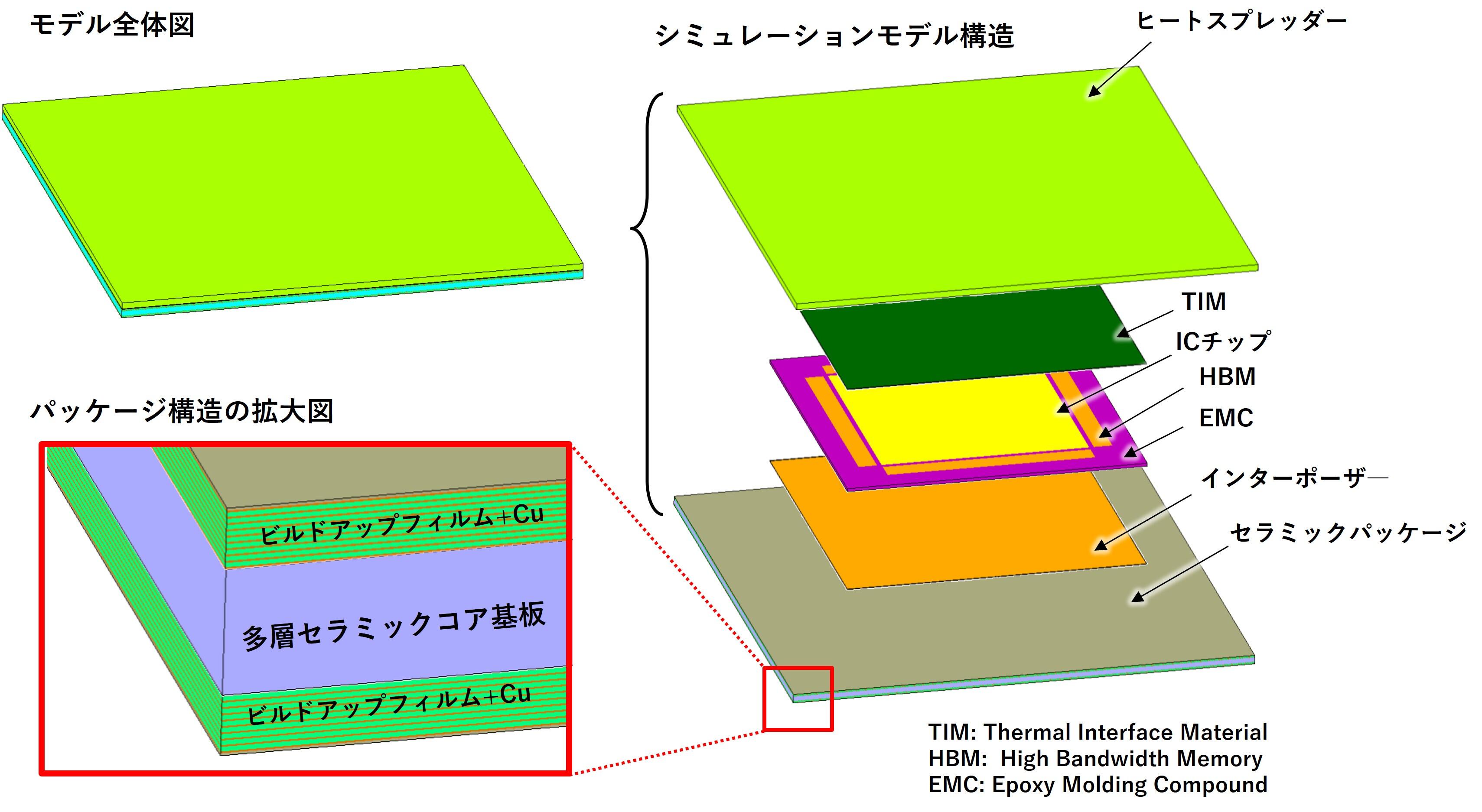

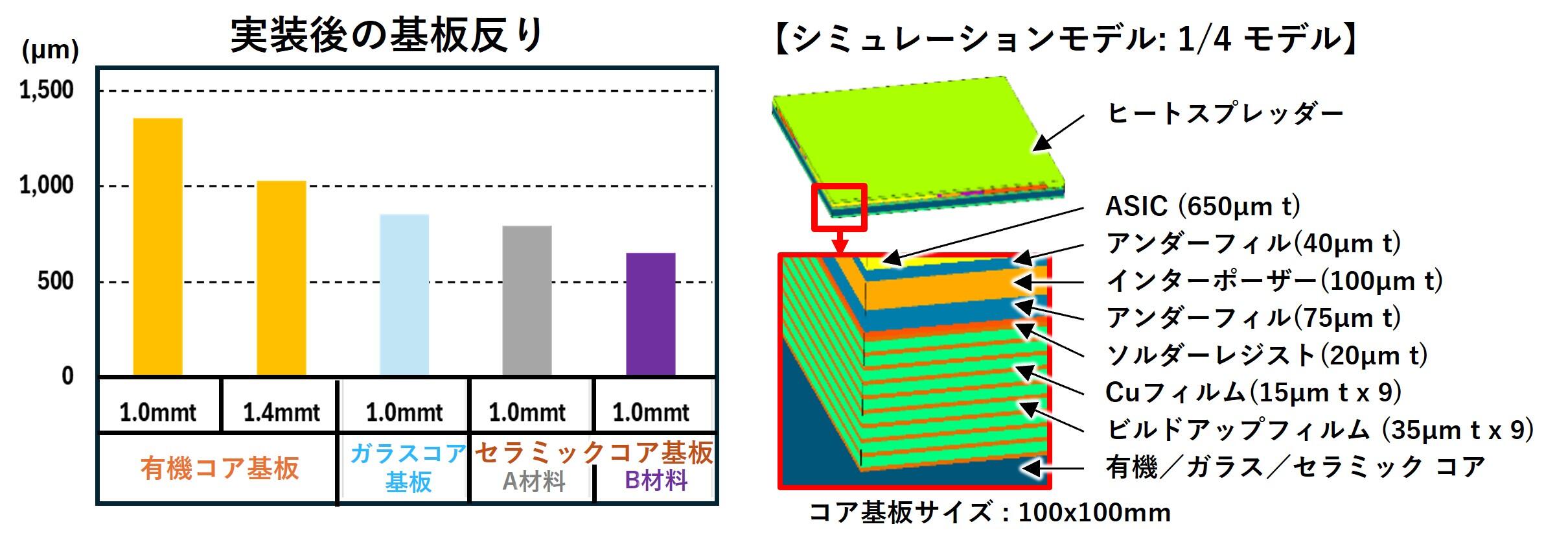

以下は、コア材に有機材料とガラス、セラミック材料を用いた際の、実装後の反り量比較をシミュレーションした結果です。

セラミック材料は、他の材料よりも反り量が小さいことが分かります。

材料特性表

※上記の材料物性値は代表値です。これらの値は、材料や工程の改善や変更によって変更されることがあります。

シミュレーションサポート

ご要望に合わせた応力/電気/熱シミュレーションでお客様の設計をサポートします。詳細は以下をご覧ください。

反りシミュレーションモデルの事例